## Improving the Performance and Energy-efficiency of Virtual Memory

### A Range-based Approach

Vasileios Karakostas

Department of Computer Architecture

Universitat Politècnica de Catalunya

A dissertation submitted in fulfillment of the requirements for the degree of Doctor of Philosophy / Doctor per la UPC April 2016

| Acta de calificación de tes                 | is doctoral                 | •                         | Curso académico:                         |

|---------------------------------------------|-----------------------------|---------------------------|------------------------------------------|

| Nombre y apellidos                          |                             |                           |                                          |

| Programa de doctorado                       |                             |                           |                                          |

| Unidad estructural responsable del programa |                             |                           |                                          |

|                                             |                             |                           |                                          |

| Decelusión del Tribunel                     |                             |                           |                                          |

| Resolución del Tribunal                     |                             |                           |                                          |

| Reunido el Tribunal designado a tal e       | efecto, el doctorand        | lo / la doctoranda        | expone el tema de la su tesis doctoral   |

| titulada                                    |                             |                           |                                          |

|                                             |                             |                           | <del>.</del>                             |

|                                             | ar respuesta a las          | cuestiones form           | nuladas por los miembros titulares del   |

| tribunal, éste otorga la calificación:      |                             | _                         | _                                        |

| NO APTO AI                                  | PROBADO                     | NOTABLE                   | SOBRESALIENTE                            |

|                                             |                             |                           |                                          |

| (Nombre, apellidos y firma)                 |                             | (Nombre, apellidos y firm | na)                                      |

|                                             |                             |                           |                                          |

| Presidente/a                                |                             | Secretario/a              |                                          |

| (Nombre, apellidos y firma)                 | (Nombre, apellidos y firma) |                           | (Nombre, apellidos y firma)              |

|                                             |                             |                           |                                          |

| Vocal                                       | Vocal                       |                           | Vocal                                    |

|                                             |                             |                           |                                          |

|                                             | _de                         | de                        |                                          |

|                                             |                             |                           |                                          |

|                                             |                             |                           |                                          |

|                                             |                             |                           |                                          |

|                                             | •                           |                           | s del tribunal, efectuado por la Escuela |

| de Doctorado, a instancia de la Comis       | sion de Doctorado d         | le la UPC, otorga         | IA MENCION CUM LAUDE:                    |

| ∐ SÍ                                        |                             |                           |                                          |

|                                             |                             |                           |                                          |

| (Nombre, apellidos y firma)                 |                             | (Nombre, apellidos y firm | na)                                      |

|                                             |                             |                           |                                          |

| Presidente de la Comisión Permanente        | a de la Escuela de          | Secretaria de la          | Comisión Permanente de la Escuela de     |

| Doctorado                                   | , de la Escuela de          | Doctorado                 | Comision i emanente de la Escuela de     |

|                                             |                             |                           |                                          |

|                                             |                             |                           |                                          |

| Barcelona a de                              | de                          |                           |                                          |

#### **Abstract**

Virtual memory improves programmer productivity, enhances process security, and increases memory utilization. These benefits are provided by introducing an indirection level between the virtual address space that the process sees and the physical memory that the operating system manages and allocates for each process. Thus, virtual memory requires an address translation from the virtual to the physical address space on every memory operation.

Page-based implementations of virtual memory divide physical memory into fixed size pages, and use a per-process page table to map virtual pages to physical pages. The hardware key component for accelerating the address translation is the Translation Lookaside Buffer (TLB), that holds recently used mappings from the virtual to the physical address space. The TLB used to be a small monolithic structure. Due to the criticality of the TLB in the system's performance, commodity processors have employed a per-core two-level TLB organization with additional support for huge pages. However, the address translation still incurs high (i) performance overheads due to costly page table walks after TLB misses, and (ii) energy overheads due to frequent TLB lookups on every memory operation. This thesis quantifies these overheads and proposes techniques to mitigate them.

In this thesis we argue that fixed size page-based approaches for address translation exhibit limited potential for improving TLB performance because they increase the TLB reach by a *fixed amount*. To overcome the limitations of such approaches, we introduce the concept of *range translations* and we show how they can significantly improve the performance and energy-efficiency of address translation.

We first comprehensively quantify the address translation performance overhead on a collection of emerging scale-out applications. We show that address translation accounts for up to 16% of the total execution time. We find that huge pages may improve the application performance by reducing the time spent in page walks, enabling better exploitation of the available execution resources. However, the limited hardware support for huge pages in combination with the workloads' low memory locality leave ample space for performance optimizations. In response, we present upper bounds for perfect optimizations

in the address translation path that motivate rethinking its design in the context of memory intensive applications.

To reduce the performance overheads of address translation, we propose *Redundant Memory Mappings (RMM)*. RMM leverages *ranges* of pages and provides an efficient alternative representation of many virtual-to-physical mappings. We define a *range translation* be a subset of a process's pages that are virtually and physically contiguous. RMM translates each range translation with a single *range table entry*, enabling a modest number of entries to translate most of the process's address space. RMM operates in parallel with standard paging and introduces a software range table and a hardware range TLB with arbitrarily large reach that is accessed in parallel with the regular L2-page TLB. We modify the operating system to automatically detect ranges and to increase their likelihood with *eager page allocation*. RMM is thus transparent to applications. We prototype RMM software in Linux and emulate the hardware. RMM reduces the overhead of virtual memory to less than 1% on average on a wide range of workloads.

To reduce the energy cost of address translation, we propose the Lite mechanism and the  $TLB_{Lite}$  and  $RMM_{Lite}$  designs. Lite is a mechanism that monitors the performance and utility of L1 TLBs, and adaptively changes their sizes with way-disabling. The resulting  $TLB_{Lite}$  organization targets commodity processors with TLB support for huge pages and opportunistically reduces the dynamic energy spent in address translation with minimal impact on TLB miss cycles. To further provide more energy-efficient address translation, we propose  $RMM_{Lite}$  that leverages the RMM address translation mechanism.  $RMM_{Lite}$  adds to RMM an L1-range TLB, that is accessed in parallel with the regular L1-page TLB, and the Lite mechanism. The high hit ratio of the L1-range TLB allows Lite to downsize the L1-page TLBs more aggressively.  $RMM_{Lite}$  reduces the dynamic energy spent in address translation by 71% on average. Above the near-zero L2 TLB misses from RMM,  $RMM_{Lite}$  further reduces the overhead from L1 TLB misses by 99%.

The proposed designs target current and future high-performance and energyefficient memory systems to meet the ever increasing memory demands of applications.

#### Acknowledgements

My "short" journey in Barcelona started with a six-month visit as part of my undergraduate studies and ends after several years with completing a PhD degree (for the moment). The journey was not short. But it was a really great experience, thanks to the support of many people that I wish to acknowledge here.

First of all, I would like to express my deepest gratitude to my advisors Mario Nemirovsky, Osman S. Unsal, and Adrian Cristal. Mario's enthusiasm and solid criticism in discussing ideas helped me a lot in identifying interesting problems and asking the right questions. His extremely positive and supportive character helped me in surpassing the obstacles that I encountered in my way. Osman and Adrian trusted me from day one, first with accepting me as an intern, and later with allowing me to continue my graduate studies at Barcelona Supercomputing Center. I sincerely thank them for their sound and technical advice, but more importantly for their immense confidence, endless help, and constant support, and for giving me the freedom to work on what I was interested in.

I also had the unique opportunity to have three exceptional external faculty collaborators that I would like to gratefully thank: Prof. Mark D. Hill, Prof. Michael M. Swift, and Prof. Kathryn McKinley. They all greatly helped me in shaping and communicating the ideas presented in this thesis. Moreover, they taught me many things about research, and contributed further into my transition from student to researcher. In particular, I feel indebted to Michael for the many technical discussions we had during his sabbatical in Barcelona, and for forming our great collaboration team. In addition, I would like to especially thank Mark, Michael, Prof. David A. Wood, and all the people from the Wisconsin Multifacet Project for making me feel more than welcomed in Madison during my short visit—an experience I will always remember.

I would like to thank Jayneel Gandhi for having the great pleasure to meet and collaborate extensively. His hard-working but also positive attitude helped me a lot with meeting difficult deadlines. I would also like to thank Jayneel for his help in this thesis, especially in the RMM work.

I would like to thank Prof. Guri Sohi, Prof. Uri Weiser, and Prof. Francisco Cazorla for serving in my thesis committee and providing very useful suggestions that improved this document.

I would like to thank all my collaborators and co-authors, and particularly Gokcen Kestor, Ibrahim Hur, and Carlos Villavieja for their help and support at the beginning of my graduate studies.

During my graduate studies I had the luck to meet and exchange ideas with many great researchers. In particular, I would like to thank Prof. Avi Mendelson and Dr. Tim Harris for always providing constructive feedback.

I would like to thank Xavier Salazar for his help and patience in preparing the documents for my scholarship applications.

I am also indebted to all my friends and colleagues from Barcelona Supercomputing Center for their support during these years. Many thanks go to Nehir Sonmez, Adria Armejach, Sasa Tomic, Vladimir Subotic, Oriol Arcas, Srdjan Stipic, Gulay Yalcin, Vesna Smiljkovic, Azam Seyedi, Nikola Markovic, Daniel Nemirovsky, Ferad Zyulkyarov, Behzad Salami, Furkan Ayar, Damian Roca, Francesco Ciaccia, Josue Quiroga, Vladimir Gajinov, Oscar Palomar, Omer Subasi, Javier Arias, Timothy Hayes, Milovan Djuric, Milan Stanic, Ivan Ratkovic, Cristian Perfumo, Paul Carpenter, Nebojsa Miletic, and Ruben Titos. I sincerely thank them all for their help and all the great moments we had together.

Finally, I would like to thank my friends and family for supporting me during all these years. My deepest thanks to Efi for her love, for being next to me, and for reminding me always that there is also a life to live. This dissertation would have not been possible without her.

## Contents

| Co | onten   | ts                                                       | 1X   |

|----|---------|----------------------------------------------------------|------|

| Li | st of 1 | Figures                                                  | xiii |

| Li | st of ' | Tables                                                   | xvii |

| Li | st of   | Algorithms                                               | xix  |

| 1  | Intr    | oduction                                                 | 1    |

|    | 1.1     | Virtual Memory                                           | 1    |

|    |         | 1.1.1 Architectural Support                              | 2    |

|    |         | 1.1.2 Evolution of Address Translation Hardware Support  | 2    |

|    | 1.2     | Motivation                                               | 3    |

|    | 1.3     | Problem Statement                                        | 4    |

|    | 1.4     | Thesis Approach                                          | 5    |

|    | 1.5     | Thesis Contributions                                     | 5    |

|    |         | 1.5.1 Quantifying Address Translation Overheads          | 6    |

|    |         | 1.5.2 Reducing Address Translation Performance Overheads | 6    |

|    |         | 1.5.3 Improving Address Translation Energy-Efficiency    | 8    |

|    | 1.6     | Thesis Organization                                      | 9    |

| 2  | Bacl    | kground on Virtual Memory                                | 11   |

|    | 2.1     | Virtual Memory                                           | 12   |

|    | 2.2     | Basic Concepts                                           | 12   |

|    | 2.3     | Architectural Support                                    | 13   |

#### **CONTENTS**

|   |     | 2.3.1   | Page Table                                  | 14 |

|---|-----|---------|---------------------------------------------|----|

|   |     | 2.3.2   | Translation Lookaside Buffer                | 19 |

|   |     | 2.3.3   | MMU cache                                   | 21 |

|   |     | 2.3.4   | Huge Pages                                  | 23 |

|   | 2.4 | Addres  | ss Translation in the Multicore Era         | 25 |

|   | 2.5 | Access  | ing memory with virtual memory              | 25 |

|   | 2.6 | Segme   | ented Virtual Memory                        | 27 |

| 3 | Qua | ntifyin | g Address Translation Performance Overheads | 31 |

|   | 3.1 | Introd  | uction                                      | 31 |

|   | 3.2 | Backgr  | ound                                        | 33 |

|   |     | 3.2.1   | Scale-out Applications                      | 33 |

|   | 3.3 | Metho   | dology                                      | 34 |

|   |     | 3.3.1   | System Setup                                | 34 |

|   |     | 3.3.2   | Huge Pages                                  | 35 |

|   | 3.4 | MMU I   | Performance Analysis                        | 38 |

|   |     | 3.4.1   | How much time is spent in TLB misses?       | 39 |

|   |     | 3.4.2   | Do Huge Pages help?                         | 40 |

|   |     | 3.4.3   | Do TLB misses affect performance?           | 42 |

|   |     | 3.4.4   | How often do TLB misses occur?              | 44 |

|   |     | 3.4.5   | What is the cost of a TLB miss?             | 45 |

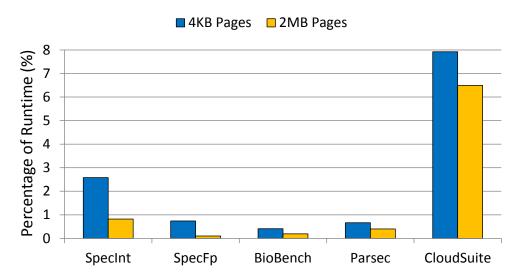

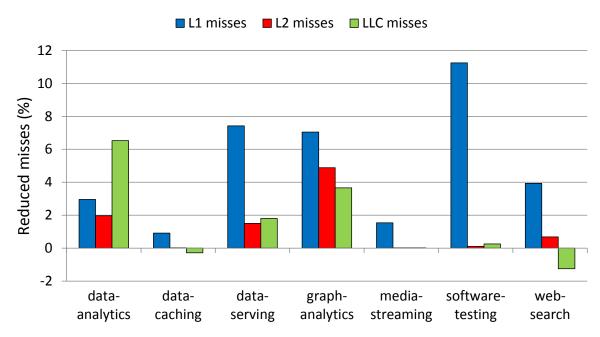

|   |     | 3.4.6   | Comparison with other benchmark suites      | 46 |

|   |     | 3.4.7   | Interference in the cache hierarchy         | 47 |

|   |     | 3.4.8   | Interaction with Hardware Prefetchers       | 49 |

|   |     | 3.4.9   | Instruction TLB misses                      | 52 |

|   |     | 3.4.10  | Summary & Implications                      | 53 |

|   | 3.5 | Potent  | ial Improvements in the MMU                 | 53 |

|   |     | 3.5.1   | Virtual Caches                              | 53 |

|   |     | 3.5.2   | Perfect MMU Caches                          | 55 |

|   |     | 3.5.3   | Perfect Cache Interference                  | 57 |

|   |     | 3.5.4   | Perfect TLBs                                | 57 |

|   | 3.6 | Relate  | d Work                                      | 58 |

|   | 3.7 | Summ    | arv                                         | 60 |

| 4 | Fast | Address Translation with Ranges 61      |     |  |  |  |

|---|------|-----------------------------------------|-----|--|--|--|

|   | 4.1  | Introduction                            |     |  |  |  |

|   | 4.2  | Background                              | 64  |  |  |  |

|   | 4.3  | Redundant Memory Mappings               | 66  |  |  |  |

|   |      | 4.3.1 Overview                          | 68  |  |  |  |

|   | 4.4  | Architectural Support                   | 69  |  |  |  |

|   |      | 4.4.1 Range TLB                         | 69  |  |  |  |

|   |      | 4.4.2 Range table                       | 71  |  |  |  |

|   |      | 4.4.3 Handling misses in the range TLB  | 73  |  |  |  |

|   | 4.5  | Operating System Support                | 74  |  |  |  |

|   |      | 4.5.1 Managing range translations       | 74  |  |  |  |

|   |      | 4.5.2 Contiguous memory allocation      | 75  |  |  |  |

|   | 4.6  | Discussion                              | 77  |  |  |  |

|   | 4.7  | Methodology                             | 79  |  |  |  |

|   | 4.8  | Results                                 | 82  |  |  |  |

|   |      | 4.8.1 Performance analysis              | 84  |  |  |  |

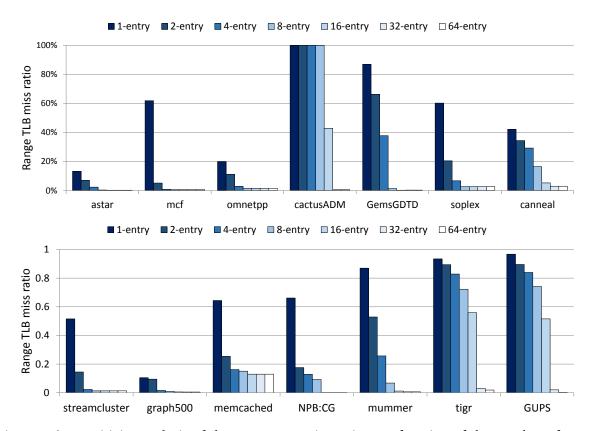

|   |      | 4.8.2 Range TLB sensitivity analysis    | 85  |  |  |  |

|   |      | 4.8.3 Impact of eager paging            | 85  |  |  |  |

|   |      | 4.8.4 Energy                            | 88  |  |  |  |

|   | 4.9  | Related Work                            | 89  |  |  |  |

|   | 4.10 | Summary                                 | 90  |  |  |  |

| 5 | Ene  | rgy-Efficient Address Translation       | 93  |  |  |  |

|   | 5.1  | Introduction                            | 93  |  |  |  |

|   | 5.2  | Background                              | 96  |  |  |  |

|   |      | 5.2.1 Trends in TLBs                    | 97  |  |  |  |

|   |      | 5.2.2 Summary                           | 97  |  |  |  |

|   | 5.3  | Energy Characterization                 | 99  |  |  |  |

|   |      | 5.3.1 Methodology Overview              | 99  |  |  |  |

|   |      | 5.3.2 Where is the energy spent?        | 99  |  |  |  |

|   |      | 5.3.3 Do huge pages help?               |     |  |  |  |

|   |      | 5.3.4 Does RMM help?                    | .02 |  |  |  |

|   |      | 5.3.5 Do larger TLB organizations help? | .02 |  |  |  |

#### **CONTENTS**

|                                   |       | 5.3.6    | Discussion                             | . 103 |

|-----------------------------------|-------|----------|----------------------------------------|-------|

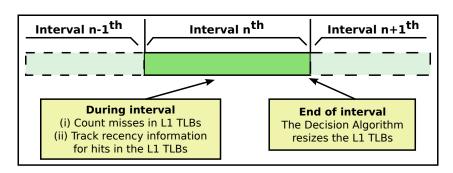

| 5.4 Efficient Address Translation |       |          |                                        | . 103 |

|                                   |       | 5.4.1    | Opportunity                            | . 103 |

|                                   |       | 5.4.2    | The <i>Lite</i> Mechanism              | . 106 |

|                                   |       | 5.4.3    | $RMM_{Lite}$ for Energy-Efficient TLBs | . 110 |

|                                   |       | 5.4.4    | Discussion                             | . 111 |

|                                   | 5.5   | Metho    | dology                                 | . 112 |

|                                   | 5.6   | Results  | 3                                      | . 117 |

|                                   |       | 5.6.1    | Dynamic Energy & Performance           | . 117 |

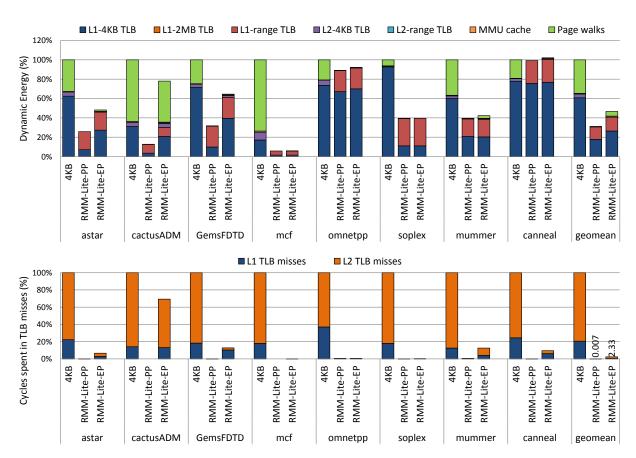

|                                   |       | 5.6.2    | Sensitivity Analysis                   | . 122 |

|                                   | 5.7   | Relate   | d Work                                 | . 124 |

|                                   | 5.8   | Summ     | ary                                    | . 126 |

| 6                                 | Con   | clusion  | s                                      | 129   |

|                                   | 6.1   | Broade   | er Impact                              | . 129 |

|                                   | 6.2   | Future   | Research Directions                    | . 130 |

|                                   | 6.3   | Furthe   | r Acknowledgements                     | . 131 |

| 7                                 | Pub   | lication | s                                      | 133   |

| Re                                | ferer | ıces     |                                        | 135   |

## List of Figures

| 2.1  | Virtual memory abstraction                                                 | 12 |

|------|----------------------------------------------------------------------------|----|

| 2.2  | Architectural support for address translation                              | 14 |

| 2.3  | Page Table                                                                 | 16 |

| 2.4  | Page table format                                                          | 17 |

| 2.5  | Translation Lookaside Buffer                                               | 19 |

| 2.6  | The TLB hierarchy.                                                         | 20 |

| 2.7  | Memory Management Unit (MMU) cache                                         | 22 |

| 2.8  | Virtual memory abstraction with huge pages                                 | 23 |

| 2.9  | TLB support for multiple pages sizes                                       | 24 |

| 2.10 | Virtual memory abstraction                                                 | 25 |

| 2.11 | Accessing memory hierarchy with virtual memory                             | 26 |

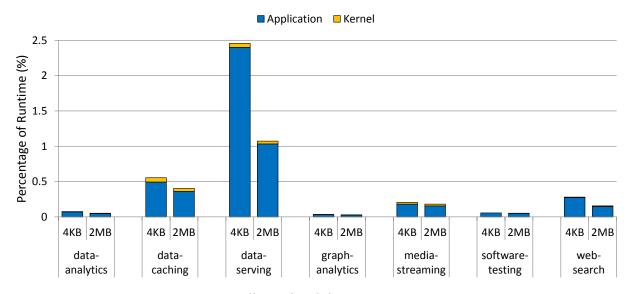

| 3.1  | Execution time spent in page walks due to data accesses with 4 KB and 2 MB |    |

|      | pages for scale-out workloads                                              | 38 |

| 3.2  | Normalized cycles spent in page walks due to data accesses with 4 KB and   |    |

|      | 2 MB pages for scale-out workloads                                         | 41 |

| 3.3  | Speedup due to increasing the page-size from 4 KB to 2 MB for scale-out    |    |

|      | workloads                                                                  | 43 |

| 3.4  | Page walks per thousand instructions due to data accesses with 4 KB and    |    |

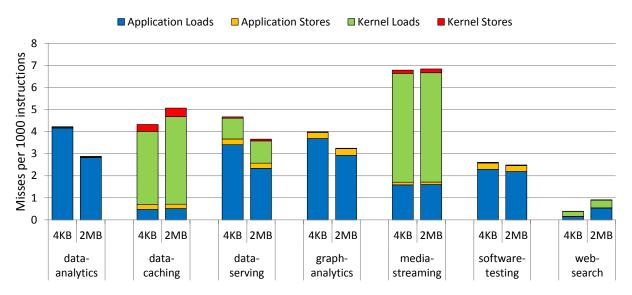

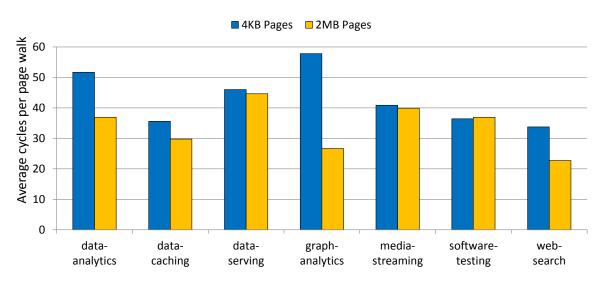

|      | 2 MB pages for scale-out workloads                                         | 44 |

| 3.5  | Average number of cycles per page walk due to data accesses with 4 KB and  |    |

|      | 2 MB pages for scale-out workloads                                         | 45 |

| 3.6  | Comparison of the MMU performance with other benchmark suites              | 47 |

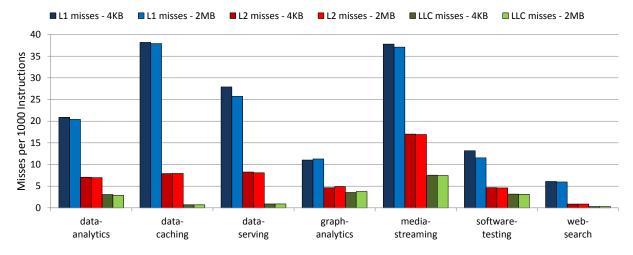

| 3.7  | Percentage of reduced cache misses (L1, L2 and LLC) due to increasing the    |     |

|------|------------------------------------------------------------------------------|-----|

|      | page-size from 4 KB to 2 MB for scale-out workloads                          | 48  |

| 3.8  | Cache misses (L1, L2 and LLC) per 1000 instructions with 4 KB and 2 MB       |     |

|      | pages for scale-out workloads                                                | 48  |

| 3.9  | Page walk overhead due to instruction TLB misses for scale-out workloads     | 52  |

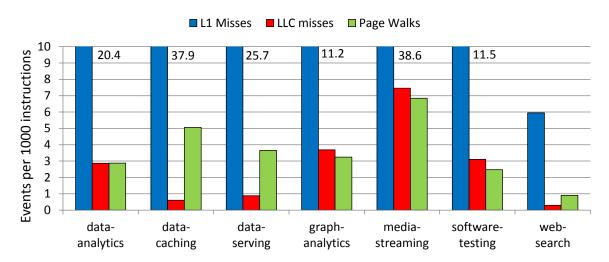

| 3.10 | Comparison of page walks and LLC misses per thousand instructions due to     |     |

|      | data accesses with 2 MB pages for scale-out workloads                        | 54  |

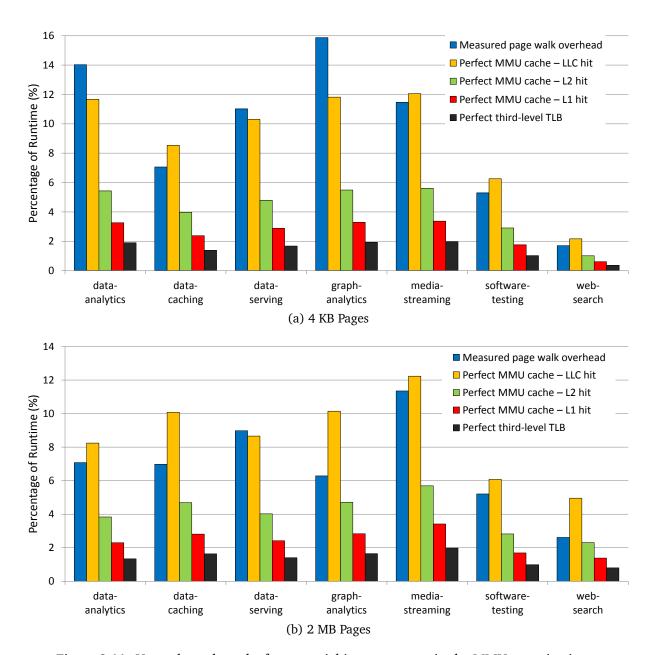

| 3.11 | Upper-bound results for potential improvements in the MMU organization       |     |

|      | for scale-out workloads                                                      | 56  |

| 4.1  | Address space layout with Redundant Memory Mappings                          | 62  |

| 4.2  | Redundant Memory Mappings design: the application's memory space is          |     |

|      | represented <i>redundantly</i> by both pages and range translations          | 67  |

| 4.3  | RMM hardware support: the Range TLB                                          |     |

| 4.4  | RMM software support: the Range Table                                        | 72  |

| 4.5  | Comparison of RMM with other schemes in reducing the execution time          |     |

|      | overheads due to page walks for various TLB-intensive workloads from Spec    |     |

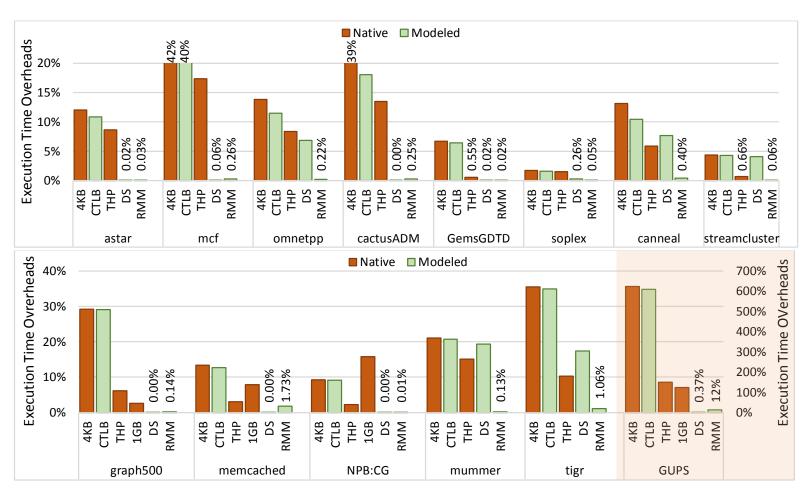

|      | 2006, Parsec, BioBench, and big-memory workloads                             | 83  |

| 4.6  | Sensitivity analysis of the range TLB miss ratio as a function of the number |     |

|      | of range TLB entries                                                         | 86  |

| 5.1  | A common per-core two-level TLB organization that supports multiple page     |     |

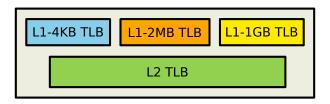

|      | sizes (4 KB, 2 MB, and 1 GB) through separate L1 TLBs                        | 94  |

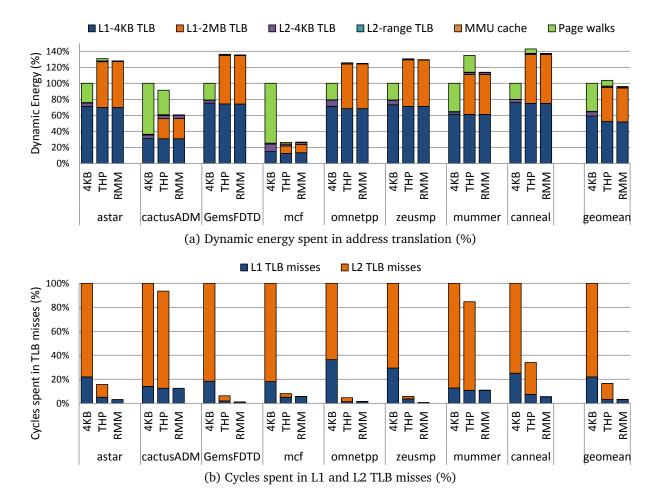

| 5.2  | Dynamic energy spent in address translation and cycles spent in TLB misses   |     |

|      | for various TLB intensive workloads with 4 KB pages, Transparent Huge        |     |

|      | Pages, and RMM                                                               | 100 |

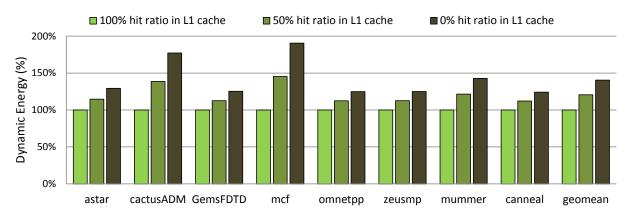

| 5.3  | Sensitivity analysis of the dynamic energy spent in address translation for  |     |

|      | various cache hit ratios for the page walk references with 4 KB pages        | 102 |

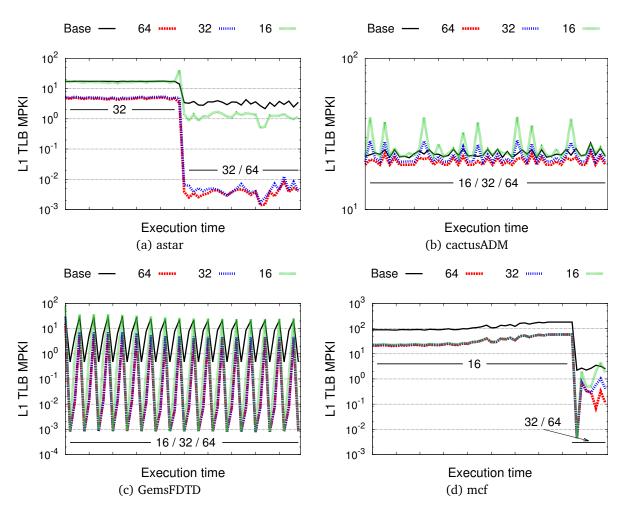

| 5.4  | Opportunity for Lite: L1 TLB misses per thousand instructions during the     |     |

|      | execution of 50 billion instructions for astar, cactusADM, GemsFDTD, and     |     |

|      | mcf, with various TLB organizations                                          | 104 |

| 5.5  | Opportunity for Lite: L1 TLB misses per thousand instructions during the     |     |

|      | execution of 50 billion instructions for omnetpp, zeusmp, mummer, and        |     |

|      | canneal, with various TLB organizations                                      | 105 |

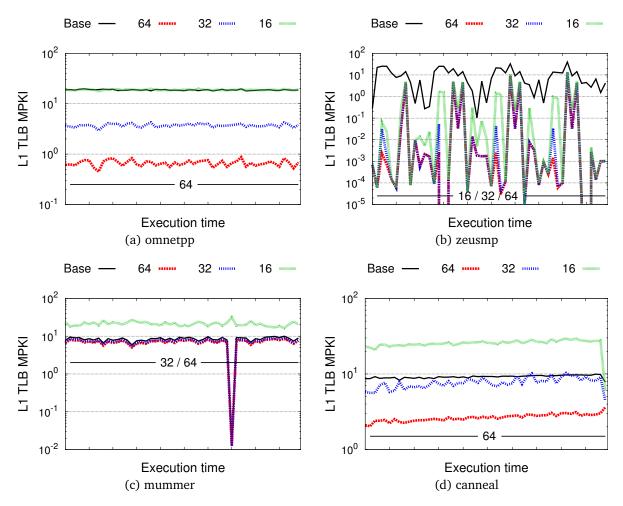

| 5.6  | Lite divides the execution time of an application into intervals 106                           |

|------|------------------------------------------------------------------------------------------------|

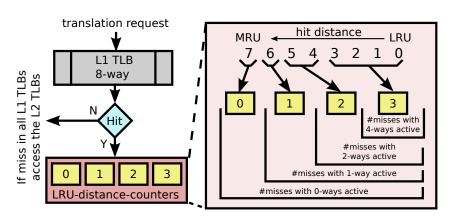

| 5.7  | Lite introduces lru-distance-counters per L1 TLB to track the utility of ways $108$            |

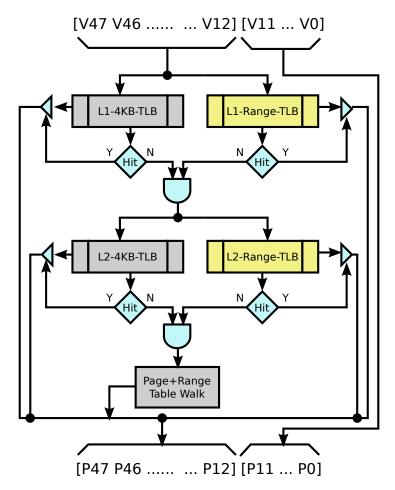

| 5.8  | $RMM_{Lite}$ introduces an L1-range TLB and Lite to the L1-page TLBs, in                       |

|      | addition to the architectural support of RMM                                                   |

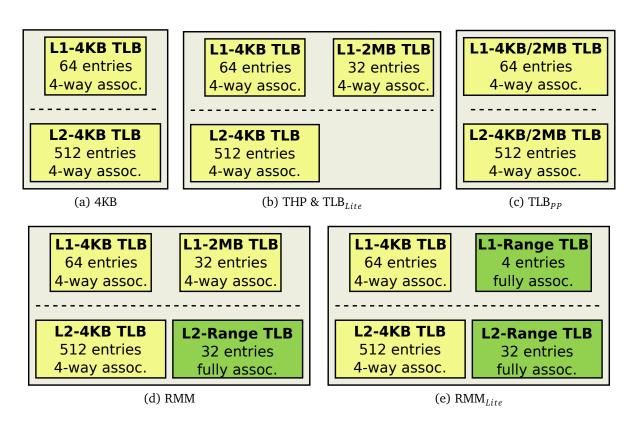

| 5.9  | TLB configurations                                                                             |

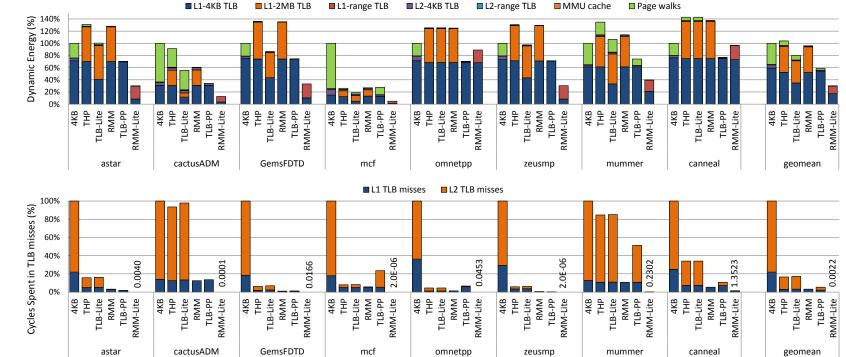

| 5.10 | Dynamic energy spent in address translation and cycles spent in TLB misses                     |

|      | for various TLB intensive workloads                                                            |

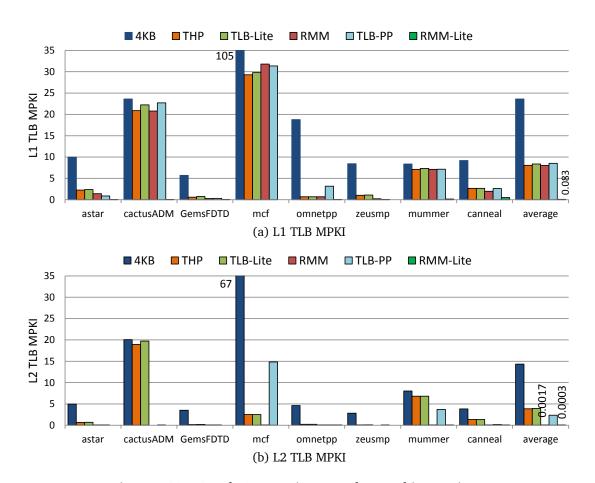

| 5.11 | $\rm L1$ and $\rm L2$ TLB misses per thousand instructions for various TLB configurations. 121 |

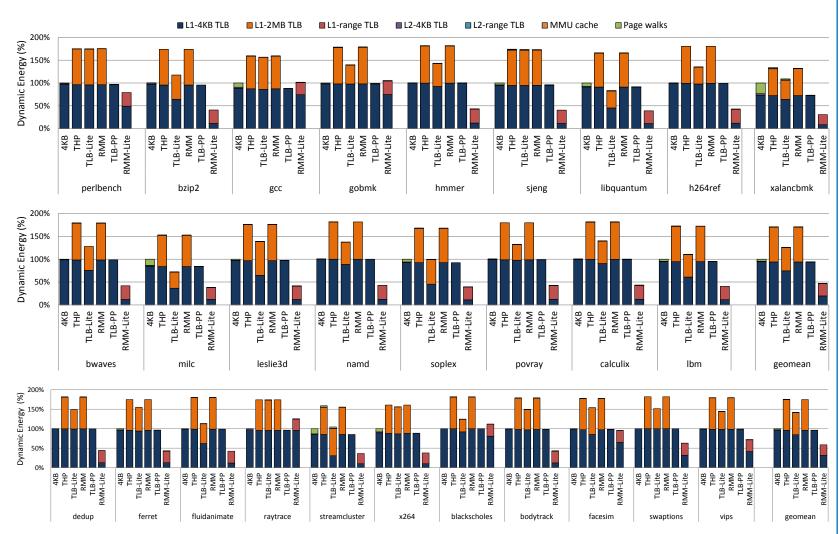

| 5.12 | Dynamic energy reduction for the rest of Spec2006 and Parsec workloads $123$                   |

| 5.13 | Dynamic energy spent in address translation and cycles spent in TLB misses                     |

|      | for $RMM_{Lite}$ with perfect eager paging and with our actual eager paging                    |

|      | implementation                                                                                 |

## List of Tables

| 3.1 | TLB hierarchy of the test machine                                                                                                                                            | 35 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Metrics and corresponding hardware performance counters                                                                                                                      | 36 |

| 3.3 | Memory usage statistics for scale-out workloads                                                                                                                              | 37 |

| 3.4 | Page walks per 1000 instructions, average cycles per page walk, and cycles spent in page walks for scale-out workloads with 2 MB pages, normalized to 4 KB pages             | 46 |

| 3.5 | Page walks per 1000 instructions, average cycles per page walk, and cycles spent in page walks for scale-out workloads with 2 MB pages for various prefetcher configurations | 51 |

| 4.1 | Comparison of Redundant Memory Mappings with previous approaches for reducing virtual memory overhead                                                                        | 65 |

| 4.2 | Comparison of required translation entries to map the application's memory with pages and ranges, for various memory intensive workloads                                     | 66 |

| 4.3 | Overview of Redundant Memory Mappings                                                                                                                                        | 68 |

| 4.4 | System configurations and per-core TLB hierarchy                                                                                                                             | 80 |

| 4.5 | Performance model                                                                                                                                                            | 81 |

| 4.6 | Workload description and memory footprint                                                                                                                                    | 82 |

| 4.7 | Impact of eager paging on ranges, time, and memory compared to demand paging with Transparent Huge Pages.                                                                    | 87 |

| 5.1 | Details of the private, per-core, data TLB hierarchy for the three latest Intel processor architectures                                                                      | 98 |

#### LIST OF TABLES

| 5.2 | Dynamic energy and leakage power for the memory structures that partici-        |

|-----|---------------------------------------------------------------------------------|

|     | pate in the address translation path                                            |

| 5.3 | Dynamic energy and performance models                                           |

| 5.4 | Workload description and memory footprint                                       |

| 5.5 | Percentage of lookups with $N$ active ways in the L1-page TLBs for $TLB_{Lite}$ |

|     | and $\mathrm{RMM}_{Lite}$                                                       |

| 5.6 | Percentage of hits in the L1 TLBs for $TLB_{Lite}$ and $RMM_{Lite}$             |

## List of Algorithms

| 4.1 | Pseudocode of memory allocation with Eager Paging | 77  |

|-----|---------------------------------------------------|-----|

| 5.1 | Pseudocode of Lite's decision algorithm           | 109 |

# Introduction

In this chapter, we first present the basic concepts of page-based virtual memory and the evolution of the address translation support. We then discuss the motivation behind our work and state the problems that we tackle in this thesis. Then we present our approach for reducing the performance and energy overheads of virtual memory, and, finally, we provide an overview of our contributions.

#### 1.1 Virtual Memory

Virtual memory provides the programmer with an "infinite" amount of memory by virtualizing the available physical memory. This functionality increases programmer productivity, enables process isolation, and enhances system consolidation.

To provide all these benefits, virtual memory introduces an indirection level between the virtual address space that each process sees and the physical memory that the operating system manages and allocates for all processes. However, the indirection cost of virtual memory does not come for free: *virtual memory implies that each memory operation made*  by an application requires an address translation to obtain the physical address, incurring high performance [27, 28, 68, 77, 90] and energy [2, 3, 49, 71, 72, 73] overheads.

#### 1.1.1 Architectural Support

Page-based implementations of virtual memory are ubiquitous in modern computing systems. They divide physical memory into fixed size pages, typically 4 KB, and use a perprocess *page table* to map virtual pages to physical pages. The page table is typically organized in an hierarchical fashion that requires multiple memory references for retrieving a virtual to physical mapping. The Memory Management Unit (MMU) is responsible for performing fast address translation in hardware, avoiding accesses in the page table. The MMU primarily consists of the Translation Lookaside Buffer.

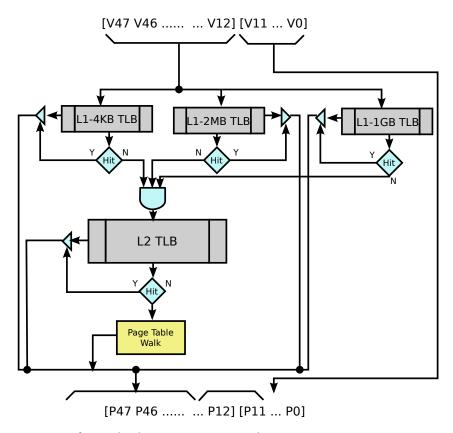

Translation Lookaside Buffer (TLB) is the hardware key component for accelerating address translation. The TLB holds recently used mappings from the virtual to the physical address space. The processor accesses the TLB on every memory request to obtain the address translation, either before or in parallel with accessing the cache hierarchy. In case of TLB hit, the address translation is obtained fast, and the memory request continues with accessing the memory hierarchy. However, in case of TLB miss, a page walk occurs, i.e., a hardware state machine walks the page table. The page walk introduces extra multiple memory references to fetch the address translation from the page table, e.g., four memory references in the x86-64 architecture. Thus, the performance of the TLB depends on the *TLB reach*, i.e., the memory for which the TLB may service address translation requests without experiencing a miss.

#### 1.1.2 Evolution of Address Translation Hardware Support

For a long time since their invention in the 1960s [44], TLBs have been a small monolithic structure and were able to deliver high performance. Commercial processors, however, keep on devoting more resources to memory and address translation to meet the ever increasing memory demands of memory intensive workloads. The common organization of the MMU found in today's processors includes: (i) per-core multi-level TLBs, (ii) with support for huge pages, (iii) backed by MMU caches.

**Two-level TLB organization.** Due to the criticality of the TLB in the system's performance, processor vendors have employed a per-core two-level TLB organization. The L1 TLB is small and features a very fast search operation to serve the processor as fast as possible. The L2 TLB is larger and slower than the L1 TLB, and aims at holding as many translations as possible in order to reduce the number of the costly page walks. To boost the system's performance further, processors provide separate TLBs for data and instruction accesses.

**TLB Support for Huge Pages.** To increase further the TLB reach and improve TLB performance, processors provide TLB support for huge pages. For example, x86-64 architectures provide TLB support for 2 MB and 1 GB pages, in addition to 4 KB pages. Thus, a single TLB entry for a huge page maps the same memory as if multiple TLB entries for regular base pages were used.

**MMU cache.** To reduce the impact of the page walk latency in performance, commercial processors back the TLB organization with MMU caches. The MMU cache reduces the cost of page walks by caching intermediate levels of the page table, while the TLB only caches the leaves of the page table. A hit in the MMU cache enables the processor to skip one or more levels of the page table in order to complete the address translation with less memory operations.

#### 1.2 Motivation

#### Mismatch Between TLBs, Memories, and Emerging Workloads

Page-based virtual memory used to deliver high performance, since TLBs serviced the vast majority of address translation requests. Unfortunately, the performance of paging is suffering. While memory sizes—both on-chip and off-chip—increase due to Moore's law, TLB sizes have merely increased within the evolution of processors with respect to memories. The reason for this mismatch is straight-forward: *TLBs are on the critical path of accessing the memory hierarchy*. Adding more entries in the TLBs may increase the hit ratio. However, the TLB latency also increases due to the larger size, affecting the translation cost for all memory operations—including TLB hits. In addition, because the TLBs are accessed on every memory reference, they consume important percentage of processor energy. Adding more entries in the TLBs will also increase their energy consumption. Consequently, the

#### 1. INTRODUCTION

TLBs remain practically stagnant with respect to memory sizes, and introduce significant performance and energy overheads for those workloads that deal with large working sets and exhibit poor memory locality. Without new designs, the mismatch between TLBs, memory sizes, and application behavior will likely keep growing.

#### 1.3 Problem Statement

Previous works have highlighted the impact of the address translation path in terms of performance and energy overheads. This thesis quantifies these overheads and proposes techniques to mitigate them.

**High Address Translation Performance Overheads.** The performance of page-based virtual memory is suffering due to *limited TLB reach*. Recent studies and this thesis show that modern workloads can experience performance overhead due to page table walks [27, 28, 68, 77, 90]. This overhead is likely to grow, because physical memory sizes are still growing.

The first goal of this thesis is to quantify the performance overhead of address translation for an emerging class of workloads, and to eliminate the performance overheads of virtual memory with a robust virtual memory implementation that is transparent to applications and that enables fast address translation across a variety of workloads.

**High Address Translation Energy Overheads.** The TLBs have been reported to consume a significant fraction of energy spent by the processor since the time they were monolithic [2, 3, 49, 71, 72, 73]. The recent growth in the complexity of the TLBs has further increased their energy consumption. A recent industrial report suggests that TLBs are responsible for 3-13% of a processor's power [108].

The second goal of this thesis is to analyze the sources of inefficiency in the address translation path, and to improve opportunistically the energy efficiency of TLBs in the presence of mechanisms that increase TLB reach while improving also the performance.

#### 1.4 Thesis Approach

Fixed size page-based approaches exhibit limited potential for improving TLB performance because they increase the TLB reach by a *fixed amount*. As memory sizes increase more aggressively than TLB sizes, we believe that the virtual memory overheads that manifest in today's systems with 4 KB pages, will manifest similarly in tomorrow's systems with larger but fixed size mappings. Our experiments show that such cases exist already.

In this thesis we take a different approach and introduce the concept of *range translations* for translating contiguous virtual pages that are mapped to contiguous physical pages. Range translations enable an efficient alternative representation of many virtual-to-physical mappings. We show that range translations can significantly reduce the performance and energy overheads spent in address translation. Hence, we argue that range translations is the next logical step in the evolution of virtual memory.

#### 1.5 Thesis Contributions

This thesis makes the following contributions:

- We quantify the performance overheads of address translation under the execution

of scale-out applications that dominate in datacenter computing. We find that a

significant percentage of the total execution time is spent in page walks due to TLB

misses, even when huge pages are employed.

- To reduce the address translation performance overheads, we propose *Redundant Memory Mappings* (RMM), a hardware/software co-designed implementation of virtual memory that reduces significantly the number of TLB misses that trigger page walks through the notion of range translations.

- To reduce the energy overheads and to provide energy-efficient address translation, we introduce the Lite mechanism, and we propose  $TLB_{Lite}$  that targets commodity processors with TLB support for huge pages, and  $RMM_{Lite}$  that builds on RMM and leverages the architectural support for ranges.

Next we highlight the most important concepts of each contribution.

#### 1.5.1 Quantifying Address Translation Overheads

Scale-out applications target various domains of datacenter computing including data analytics, key-value caching and storing, graph analytics, and web-searching, among others. These applications operate on large datasets with low memory locality, exhibiting inefficient execution in traditional server architectures [50]. In response, researchers proposed novel designs to increase the efficiency of various components of the microprocessors for scale-out applications [69, 86, 87]. However, the performance overhead of address translation in the Memory Management Unit (MMU) for scale-out applications has been largely ignored. There have been very few studies that primarily focused on solutions to mitigate the performance cost of the MMU [27, 28].

In this thesis, we perform a comprehensive performance analysis of the MMU under the execution of various scale-out applications. We conduct our analysis leveraging the use of performance counters on an x86-64 real system.

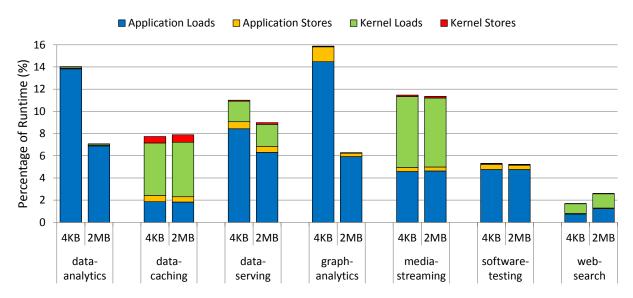

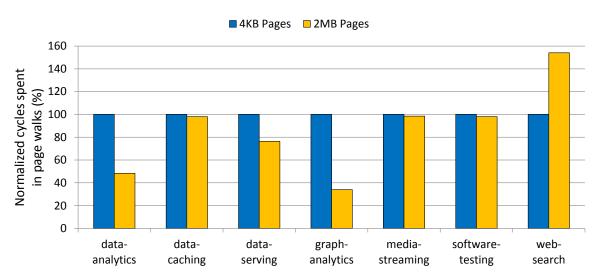

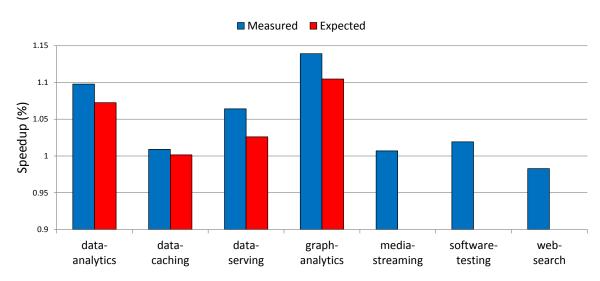

We find that the performance overhead of address translation accounts for up to 16% of the total execution time, due to the high number of TLB misses that trigger page walks and the interference between page walks and application data in the cache hierarchy. We find that the performance improves by reducing the time spent in page walks, enabling better exploitation of the available execution resources.

We observe that huge pages are beneficial for most applications without being an "always-win" option due to limited hardware support. We also quantify the interference between the application data and the page table in the cache hierarchy, and show how page walks are affected by hardware prefetchers.

Finally, we present upper-bound analyses and provide potential directions for improving the MMU performance.

#### 1.5.2 Reducing Address Translation Performance Overheads

Page-based virtual memory incurs high performance overheads due to costly page table walks after TLB misses. Previous research has aimed on increasing TLB reach by improving the efficiency of paging with: (i) Multipage mappings [96, 97, 111], that translate several pages with a single TLB entry, (ii) Huge pages [5, 8], that translate much larger aligned memory with a single TLB entry, and (iii) Direct segments [27, 52], that provide a single arbitrarily large segment along with standard paging. However, all these efforts suffer

from various limitations; multipage mappings and huge pages have size and alignment restrictions, and still provide limited TLB reach with respect to the ever-growing physical memories, while direct segments require application modifications and do not provide performance benefits for all workloads.

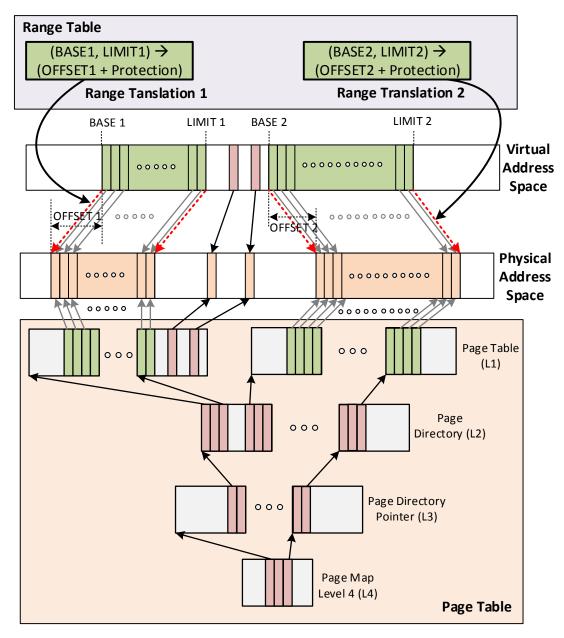

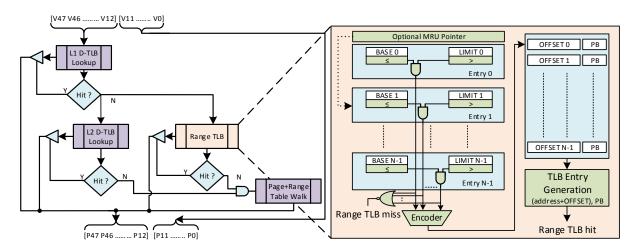

In this thesis, we propose *Redundant Memory Mappings* (RMM), a novel hardware/software co-designed implementation of virtual memory. RMM exploits the natural contiguity in address space and introduces a redundant mapping named *range translation*, in addition to page tables, that provides a more efficient representation of translation information for *ranges* of pages that are both virtually and physically contiguous with uniform protection. With range translations, RMM increases the TLB reach and reduces significantly the number of page walks, enabling a robust virtual memory implementation with near zero performance overhead.

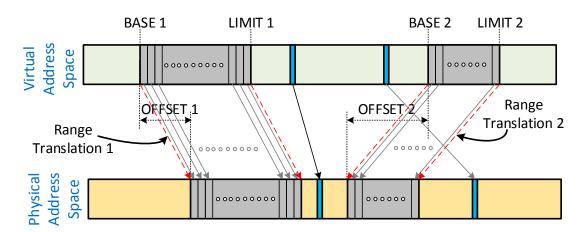

RMM relies on the concept of *range translation*. Each range translation maps a contiguous virtual address range to contiguous physical pages with uniform protection access rights, and uses BASE, LIMIT, and OFFSET values to perform translation of an arbitrary sized range. Range translations are only base-page-aligned and redundant to paging; the page table still maps the entire virtual address space.

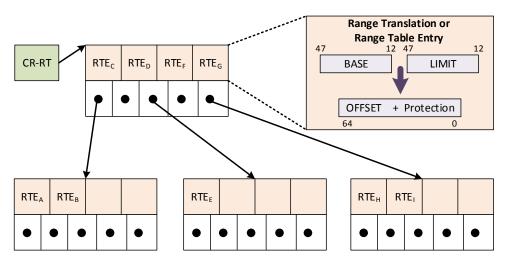

Analogous to paging, RMM introduces three novel components to perform address translation with range translations: (i) range TLBs, (ii) range tables, and (iii) eager paging allocation. More specifically, RMM introduces a hardware range TLB that is accessed in parallel with the L2-page TLB. The range TLB caches recently used range translations, accelerates their address translation, increases TLB reach, and reduces the number of page walks. RMM introduces also a software managed range table that stores in memory all range translations for each process. To increase contiguity in range translations, we extend the operating system's default lazy demand page allocation strategy to perform eager paging. Eager paging instantiates pages in physical memory at allocation request time, rather than at first-access time as with demand paging. Because range tables are redundant to page tables, RMM offers all the flexibility of paging and the operating system may use or revert solely to paging when necessary. The resulting operating system automatically maps most of process's virtual address space with orders of magnitude fewer ranges than paging.

Overall, RMM reduces the overhead of virtual memory to less than 1% on average, while combining the benefits and surpassing the limitations of previous proposals.

#### 1.5.3 Improving Address Translation Energy-Efficiency

Page-based virtual memory incurs also high energy overheads because the TLB is accessed on every memory operation. Prior research has focused on reducing the dynamic energy of TLBs through various techniques [20, 21, 38, 38, 41, 49, 71, 82]. However, those energy optimization techniques do not take into account hardware support for increasing the TLB reach (e.g., huge pages).

In this thesis, we analyze the energy spent in the address translation path, using as baseline a common per-core two-level TLB organization with a separate set-associative L1 TLB for each supported page size, e.g., for 4 KB, 2 MB, and 1 GB pages. Our findings show that the L1 TLBs are the primary source of dynamic energy overhead in the address translation path. We also find that page walks consume significant amount of energy with 4 KB pages. While huge pages and other techniques that increase TLB reach [27, 51, 78, 96, 97, 111] reduce the energy due to page walks, we observe that the "innocent" L1 TLB hits remain the dominant source of dynamic address translation, because *multiple separate L1 TLBs are accessed on every memory operation*.

To reduce the energy cost of address translation, we first propose Lite. Lite monitors the utility of ways in the L1 TLBs for each page size in an interval fashion based on the distance of TLB hits from the least-recently-used (LRU) position, similar to the accounting cache [47] and utility-based cache partitioning [102]. At the end of each interval, Lite evaluates the utility of L1 TLBs. In case the utility of active ways is insignificant, Lite opportunistically downsizes each of the L1 TLBs individually by disabling ways [16]. Lite thus accesses fewer ways in the L1 TLBs, saving energy at the cost of introducing a few additional misses. The resulting  $TLB_{Lite}$  organization targets commodity processors with TLB support for huge pages, requires minimal modifications, and opportunistically reduces L1 TLB energy with negligible impact on performance.

We additionally propose  $RMM_{Lite}$  to further augment the potential of Lite for reducing the energy in L1 TLBs while at the same time reducing both the energy and performance overheads due to L1 TLB misses.  $RMM_{Lite}$  builds on RMM, and introduces a small L1-range TLB and the Lite resizing mechanism. The L1-range TLB is accessed in parallel with the L1-page TLB and is small (e.g., 4 entries) in order to meet the tight timing requirements of L1-TLBs. Yet the L1-range TLB is powerful; each range TLB entry can hold a mapping of unlimited size, that enables the L1-range TLB to enjoys a high hit ratio. That allows Lite to

downsize L1-page TLBs more aggressively without affecting the performance.

Our evaluation results show that  ${\rm TLB}_{Lite}$  reduces opportunistically the dynamic energy spent in address translation by 23% while slightly increasing the cycles spent in TLB misses compared to huge pages [5].  ${\rm RMM}_{Lite}$  reduces the dynamic energy spent in address translation by 71% on average compared to huge pages. Above the near-zero L2 TLB misses from RMM,  ${\rm RMM}_{Lite}$  further reduces the overhead from L1 TLB misses by 99%.

Overall,  $TLB_{Lite}$  and  $RMM_{Lite}$  improve both energy efficiency and performance of address translation.

#### 1.6 Thesis Organization

Chapter 2 provides additional background on virtual memory and address translation with emphasis on page-based systems with hardware-managed TLBs.

Chapter 3 analyzes the performance of the Memory Management Unit under scale-out workloads, focusing on the cost of TLB misses that trigger page walks and their interaction with other processor components. This chapter follows mostly from our work published in 2014 IEEE International Symposium on Workload Characterization (IISWC 2014) [77].

Chapter 4 presents Redundant Memory Mappings (RMM), a hardware/software codesigned implementation of virtual memory that eliminates the number of page walks. This chapter follows mostly from our work published in the 42nd International Symposium on Computer Architecture (ISCA 2015) [78] and summarized in the IEEE Micro Special Issue on Top Picks from 2015 Computer Architecture Conferences [53].

Chapter 5 presents the Lite mechanism, and the  ${\rm TLB}_{Lite}$  and  ${\rm RMM}_{Lite}$  organizations that improve the energy-efficiency of address translation. This chapter follows mostly from our work published in the 22nd International Symposium on High Performance Computer Architecture (HPCA 2016) [79].

Chapter 6 concludes this thesis and points to future research directions.

2

## Background on Virtual Memory

This chapter provides background information on virtual memory. More specifically, we introduce the basic concepts of page-based virtual memory and the role of address translation, then we describe the software and hardware components of the architectural support for virtual memory, and finally we discuss briefly the variation of segment-based virtual memory. Since in this thesis we mainly focus in the x86-64 architecture, we explain here in more detail how address translation is performed in that architecture. Note that the problems that we tackle in this thesis are not specific to the implementation of virtual memory in the x86-64 architecture, i.e., high performance and energy overheads due to address translation, and that similar issues hold for other architectures as well. For more information about the implementation of virtual memory in other architectures, we refer the interested readers to [66, 67].

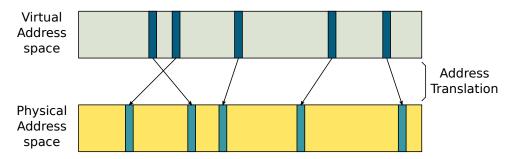

Figure 2.1: The abstraction of the page-based virtual memory. The virtual and the physical address spaces are divided into pages. The application "sees" the virtual address space. The operating system manages the physical address space. The address translation implements the abstraction of virtual memory with mapping the virtual addresses to physical addresses.

#### 2.1 Virtual Memory

Virtual memory was originally introduced in the computing systems to overcome the problem of limited physical memory. Without virtual memory, the programmer had to make sure that the program fitted in the physical memory. This restriction was responsible for decreased software productivity and limited software portability. With virtual memory, the programmer sees a big flat memory without bothering about the actual implementation and limitations of the physical memory or memory system.

Virtual memory provides several benefits that have rendered its presence ubiquitous in the computing systems for several decades now. Among others, virtual memory improves process isolation and security and enhances programmer productivity, since the operating system manages the mappings from the per-process virtual address space to the system's physical address space. In addition, virtual memory enables the operating system to consolidate more efficiently multiple running processes by managing better the available physical memory.

#### 2.2 Basic Concepts

The abstraction of page-based virtual memory relies on four basic concepts, as shown in Figure 2.1: the *virtual address space*, the *physical address space*, the *pages*, and the *address translation*. Next we introduce these basic concepts.

**Virtual address space.** The virtual address space is a set of address areas that the process sees. The operating system allocates these virtual address areas and makes them available to the process.

**Physical address space.** The physical address space is the actual physical memory, i.e., the main memory that a computing system is equipped with. The operating system manages the physical memory and allocates portions of the available physical memory to map parts or the entire virtual address space of a process.

**Pages.** Both virtual and physical address spaces are divided and managed in fixed size pages or in page granularity. The typical base size of pages for most architectures is 4 KB. The virtual address space is divided into uniform virtual pages, each of which is identified by a virtual page number. Similarly, the physical address space or physical memory is divided into uniform physical pages, each of which is identified by a physical page number or physical frame number.

Address Translation. When a process requests to access a memory location, an address translation from the virtual address space to the physical address space needs to be performed. The address translation is the function that provides that virtual-to-physical mapping; it receives as input a virtual page number, or simply a virtual address, and produces as output a physical page number, or simply a physical address. Based on the physical address, the process accesses the requested memory location and reads or writes data. Because the process always "sees" the virtual memory only, an address translation is necessary on every memory reference.

#### 2.3 Architectural Support

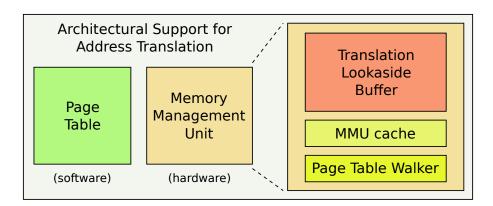

The implementation of virtual memory is a great example of hardware/software co-design between the processor (hardware) and the operating system (software). The operating system allocates physical memory, and maps the virtual addresses of a process to physical addresses by keeping the translation information in a software structure called *Page Table*. The processor accelerates virtual memory with the *Memory Management Unit (MMU)*. The MMU consists of two kinds of special address translation caches: the *Translation Lookaside Buffer (TLB)* that holds recently used page table entries, and the *MMU cache* that holds

Figure 2.2: The architectural support for address translation consists of the Page Table (software component) and the Memory Management Unit (hardware component). The MMU consists of the Translation Lookaside Buffer, the MMU cache, and the page table walker.

intermediate levels of the page table. Figure 2.2 shows the basic components of the architectural support for address translation.

#### 2.3.1 Page Table

The page table implements the abstraction between the virtual and the physical address space. The page table is an architecture-visible software data structure that is managed by the operating system. The page table stores in memory all the translations from the virtual to the physical address space for each process.

Page Table Entry (PTE). The page table consists of the page table entries. Each page table entry contains information for a virtual page that is (potentially) mapped by a physical page. This information is kept in a compact way, in order to keep the size of the page table entry reasonable and to prevent the page table itself from occupying the physical memory. The most common information found inside the page table entry across various architectures usually includes:

- the *valid bit* that indicates whether that page is actually mapped in the physical address space, and thus this page table entry holds valid information,

- the physical page number that holds the actual address translation of the corresponding virtual page,

- the *protection access rights* that define what memory operations are permitted in that page, e.g., no access, read-only access, or read/write access is permitted,

- the *privilege access level* that indicates whether user code or supervisor code can access that page,

- the *no-execute bit* that indicates whether that page may hold any code information or not, to prevent malicious software from inserting code into a data section and running their own code,

- the *cache-disabled bit* that defines whether that page is cacheable in the memory hierarchy or not,

- the *access bit* that indicates whether that page was recently accessed; the operating system uses this information to decide which pages to reclaim from the processes when serving new memory allocation requests, and

- the *modify bit* that indicates whether the processor wrote any data in that page; when set, the operating system writes back the contents of that page to the disk before reclaiming it from a process (i.e., swapping).

Hierarchical Page Table Organization. The page table could be organized as a flat table that holds all the mappings from the virtual to the physical address space for every process, including those mappings that correspond to currently non-allocated pages. However, such an organization would be clearly inefficient because it would waste a lot of memory for the page table itself.

To overcome the limitations of a flat table, the page table is usually organized in an hierarchical fashion<sup>1</sup>. The hierarchical page table organization splits the page table in various levels, so that entries in higher levels (closer to the root of the page table) hold information for larger regions of memory. Thus, the size of the hierarchical page table depends on the number of the virtual pages that a process uses.

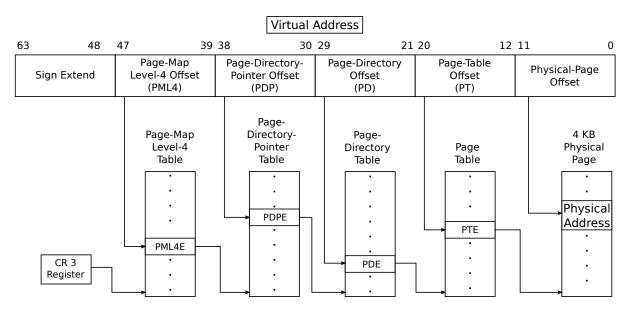

Figure 2.3 shows the implementation of the page table for the x86-64 architecture. The page table is implemented in four levels named as PML4, PDP, PD, and PT. Figure 2.4 shows

<sup>&</sup>lt;sup>1</sup>Another approach for organizing the page table is the inverted page table that is used in the PowerPC architecture [66, 67].

Figure 2.3: The design of the page table in x86-64 architecture. The page table is organized in a four-level hierarchical fashion, and thus address translation requires four memory operations.

the fields for each level of the page table. The virtual address is divided into parts and each part serves as index in that level's page table. The entries of each level hold pointers to the entries of the next level. The last-level PT of the page table (PTE) holds the translation information for that virtual address. Hence, each PT entry holds translation information for a single 4KB page of physical memory, each PD entry points to a PT and may hold translation information for a 2 MB memory area, each PDP entry points to a PD and may hold translation information for a 1 GB memory area, and each PML4 entry points to a PDP and may hold translation information for a 512 GB memory area.

**Page Walk.** Page walk is the process that involves: (i) accessing the page table with the virtual address, (ii) traversing the page table, and (iii) obtaining eventually the corresponding page table entry that contains the address translation for that virtual address. The x86-64 architecture walks the hierarchical page table in a *top-down* fashion<sup>2</sup>. The walk is performed by the page table walker, a hardware finite state machine as explained next.

The physical address of the root of the page table is stored in the *process control block*, a per-process data structure that the operating system uses to hold various information

<sup>&</sup>lt;sup>2</sup>Another approach for accessing the hierarchical page table is the bottom-up method that is used in MIPS and Alpha architectures [66, 67].

| 6<br>3  |                  |          |       |                                                   |                                                            |          |                 | 2 1 0                  | bits     |                            |                     |                             |

|---------|------------------|----------|-------|---------------------------------------------------|------------------------------------------------------------|----------|-----------------|------------------------|----------|----------------------------|---------------------|-----------------------------|

|         |                  | Reserved |       | Address of PML4 table                             |                                                            |          | Ignored PP DT   |                        | lgn.     | CR3                        |                     |                             |

| X<br>D  | Iģ               | gnored   | Rsvd. | Address o                                         | Address of page-directory-pointer table Ign. $R_{d}^{S}gA$ |          |                 |                        | CW.      | J R<br>/ / <u>1</u><br>5 W | PML4E:<br>present   |                             |

|         | Ignored <u>0</u> |          |       |                                                   |                                                            |          |                 |                        |          | PML4E:<br>not<br>present   |                     |                             |

| X<br>D  | Prot.<br>Key     | Ignored  | Rsvd. | Address<br>of 1GB<br>page frame                   | Reser                                                      | ved      | P<br>A Igi<br>T | n. G                   | 1 DA     |                            | R<br>/ 1<br>SW      | PDPTE:<br>1GB<br>page       |

| X<br>D  |                  | Ignored  | Rsvd. | A                                                 | I PPUR                                                     |          |                 |                        |          |                            | R<br>S/1            | PDPTE:<br>page<br>directory |

|         |                  |          |       |                                                   | Ignored                                                    |          |                 |                        |          |                            | 0                   | PDTPE:<br>not<br>present    |

| X<br>D  | Prot.<br>Key     | Ignored  | Rsvd. |                                                   | dress of<br>lage frame                                     | Reserved | P<br>A<br>T     | n. G                   | 1 DA     | P P I<br>CW/<br>DT/        | JR<br>SW1           | PDE:<br>2MB<br>page         |

| X<br>D  | I                | Ignored  | Rsvd. | Address of page table   Ign. $ \Omega g A C W G $ |                                                            |          |                 |                        | R<br>S/1 | PDE:<br>page<br>table      |                     |                             |

| Ignored |                  |          |       |                                                   |                                                            |          |                 |                        | 0        | PDE:<br>not<br>present     |                     |                             |

| X<br>D  | Prot.<br>Key     | Ignored  | Rsvd. | Address of 4KB page frame Ign. GADACWS/           |                                                            |          |                 |                        |          | R<br>S/1                   | PTE:<br>4KB<br>page |                             |

|         | Ignored          |          |       |                                                   |                                                            |          | 0               | PTE:<br>not<br>present |          |                            |                     |                             |

Figure 2.4: Format of the CR3 register and of the page table's entries of each level (PML4, PDP, PD, PT) for the x86-64 architecture [64]. M: the size of the physical address space, e.g., 48- to 52-bits. R/W: read/write bit. U/S: user/supervisor bit. PWT: page write through bit. PCD: page cache disable bit. A: accessed bit. D: dirty bit. G: global bit. XD: execute-disable bit.

for each process in the system. When the operating system schedules a process to a core (context switch), the OS copies also the physical address of the root of the page table in the CR3 register, an architecture-visible register. The hardware state machine uses the CR3 register to walk the page table when TLB misses occur.

Figure 2.3 shows the process of page walk for the x86-64 architecture, i.e., translating a virtual address to a physical address with the page table. The CR3 register points to the root of the PML4 table. The hardware walker uses the CR3 register as base, that points to the root of the PML4 table, and the 47-39 bits of the virtual address as index in the PML4 table to read the corresponding PML4 entry (first memory operation). That PML4 entry points to the root of a PDP table; the hardware walker uses the 38-30 bits of the virtual address as index in the PDP table to read the corresponding PDP entry (second memory operation). That PDP entry points to the root of a PD table; the hardware walker uses the 29-21 bits of the virtual address as index in the PD table to read the corresponding PD entry (third memory operation). Finally, that PD entry points to the root of a PT table; the hardware walker uses the 20-12 bits of the virtual address as index in the PT table to read the corresponding PT entry (fourth memory operation).

Page Fault. A page fault occurs when no page table entry or no valid translation is found in the page table, or when the process performs a memory operation that violates the access rights (e.g., read/write, user/supervisor, etc.) of that page. The page fault triggers an interrupt and the control is passed to the operating system that executes the page fault handler. The page fault handler is a software routine that first checks the reason that triggered that page fault, and then takes the corresponding action. In case the page fault was due to accessing for the first time a page that is allocated in the virtual address space but is not allocated yet in the physical address space (due to *demand paging*), then the operating system allocates a physical page and updates the corresponding page table entry. In case the page fault was due to accessing the backing storage (e.g., disk), then the operating system fetches the corresponding data from the backing storage into memory and updates the page table. Finally, in case the page fault was due to illegal access because of protection rights violation, then the operating system terminates the process with an error signal.

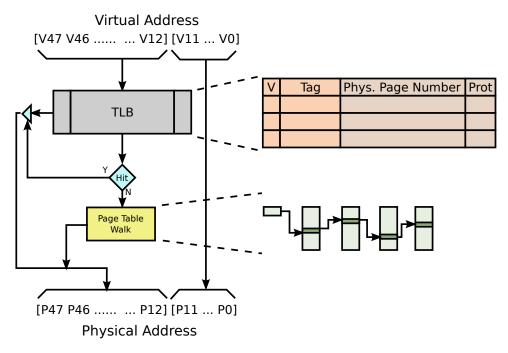

Figure 2.5: The Translation Lookaside Buffer accelerates address translation by caching recently used page table entries. In case of TLB miss, a hardware state machine walks the page table.

#### 2.3.2 Translation Lookaside Buffer

With virtual memory, each memory operation made by a process requires an address translation to obtain the physical address. This would imply that for each memory operation in the x86-64 architecture, the processor should: (i) first perform four additional memory operations to obtain the physical address from the page table, and (ii) then perform the actual memory operation that was requested in the first place. Clearly such an approach would have high impact in the performance that would probably outweigh the benefits of virtual memory.

To accelerate virtual memory, processors employ the *Translation Lookaside Buffer (TLB)*. The TLB is a small cache that only holds recently used page table entries. With respect to Figure 2.3, the TLB holds mappings from virtual pages to physical pages bypassing the intermediate levels of the page table. The processor accesses the TLB on every memory operation with the requested virtual address. In case of a hit, the TLB returns to the processor the corresponding physical address, and the processor proceeds with accessing the memory hierarchy. Thus, a TLB hit provides fast address translation without accessing the page table, as shown in Figure 2.5.

Figure 2.6: To increase TLB reach, processors have employed an hierarchical two-level TLB organization. The L1 TLB is small, set or fully associative, and features a very fast search operation, while the L2 TLB is larger and aims at holding more translations.

In case of a TLB miss, a page walk occurs that fetches from the page table the missing address translation. The page walk can either be performed in hardware (*hardware-managed TLB*) or in software (*software-managed TLB*). The x86-64 architecture uses hardware-managed TLB, and thus the page walk is performed by a hardware finite state machine or simply hardware walker. The hardware state machine walks the page table, finds the missing page table entry, and copies it in the TLB so that future memory references that access the same page will hit in the TLB. During the page walk, the pipeline continues with executing instructions that are independent of the instruction that caused that TLB miss [66, 67].

**TLB Reach.** The performance of the TLB depends on the *TLB reach*, i.e., the total amount of memory for which the TLB may service address translation requests without experiencing a miss. Because TLB address translation is on the processor's critical path, it requires low access times which constrain TLB size, and thus the TLB reach.

Hierarchical TLBs. The TLB used to be a small monolithic structure with high or fully-associative index methods. Due to the criticality of the TLB in the system's performance and energy, processor vendors have employed an hierarchical two-level TLB organization, similar to the cache hierarchy. Figure 2.6 shows an hierarchical TLB organization: the L1 TLB is small, set or fully associative, and features a very fast search operation, while the L2 TLB is larger and aims at holding more translations. To boost the system's performance further, processors provide separate TLBs for data and instructions. Note that in this thesis we use the term "TLB" to refer either to the general structure of the TLB or to the TLB hierarchy as a whole depending on the context, whereas we use the terms "L1 TLB" or "L2 TLB" to refer explicitly to that (L1 or L2) level's TLBs.

**Updating TLB entries.** The TLB is a read-only hardware structure that never holds dirty data. When the operating system changes the translation information for a page, e.g., due to relocating that page or due to changing that page's protection access rights, the TLB needs to be updated. This happens with the following procedure: the operating system (i) issues the INVLPG instruction to invalidate the stale virtual to physical translation, and (ii) updates the corresponding entries in the page table. Hence, the next memory reference in that page will cause a TLB miss, the hardware state machine will walk the page table and will install correctly the updated translation entry in the TLB.

**Summary.** The TLB is the hardware key component for accelerating virtual memory. The TLB accelerates address translation and is on the critical path of every memory operation. Due to its important functionality, the TLB performance (hit/miss ratio) affects significantly the total performance [27, 28, 68, 77, 90] and energy consumption [2, 3, 49, 71, 72, 73] of the processor.

#### 2.3.3 MMU cache

To minimize the performance overhead of the TLB misses that trigger page walks, processors have employed MMU caches [23, 28]. The MMU cache reduces the cost of page walks by caching intermediate levels of the page table, i.e., entries from the PML4, PDP, and PD levels.

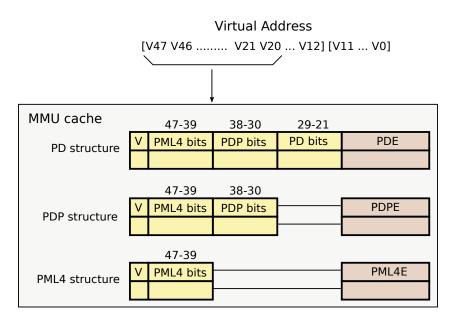

Figure 2.7 shows the design of MMU cache for the Intel x86-86 processors. The MMU cache is organized into three individual structures; the PD-structure is tagged with the 47-

Figure 2.7: The Memory Management Unit (MMU) cache reduces the cost of page walks by caching intermediate levels of the page table.

21 bits, the PDP-structure is tagged with the 47-30 bits, and the PML4-structure is tagged with the 47-39 bits. The hardware walker accesses all structures of the MMU cache with the missing-in-the-TLB virtual address. A hit in the MMU cache enables the hardware walker to skip one or more levels of the page table. The lookup request in the MMU cache may generate three hits, one for each structure; the hardware walker chooses that hit with the longest prefix that enables skipping most levels of the page table. Thus, a page walk requires between one and four memory operations to retrieve the missing address translation, based on the contents of the MMU cache; one memory operation in case of hit in the PDP-structure, two memory operations in case of hit in the PDP-structure, three memory operations in case of hit in the PML4-structure, and four memory operations in case of a complete miss in all structures of the MMU cache.

Note that the memory hierarchy may also cache any level of the page table. For example, Intel processors may cache the page table in any level of the memory hierarchy, up to the L1 cache. The difference between the MMU cache and the memory hierarchy in caching page table contents lies in the purpose they serve. The MMU cache defines the number of memory operations per page walk and the hardware walker accesses the memory hierarchy for that many times to retrieve the missing page table entry. The memory

Figure 2.8: Virtual memory abstraction with huge pages.

hierarchy holds close to the processor the contents of the page table to accelerate each page walk reference made by the hardware walker.

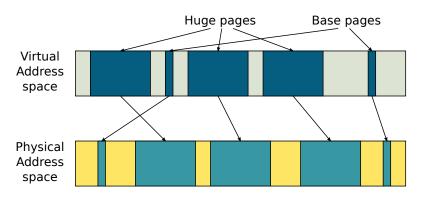

## 2.3.4 Huge Pages

To improve the limited TLB reach that 4 KB pages provide, most architectures provide support for multiple page size through *large* or *huge pages*. For example, the x86-64 architecture supports mixing 4 KB with 2 MB and 1 GB pages, while other architectures support more sizes [91, 101, 107]. Figure 2.8 shows the abstraction of virtual memory that supports both base pages and huge pages.

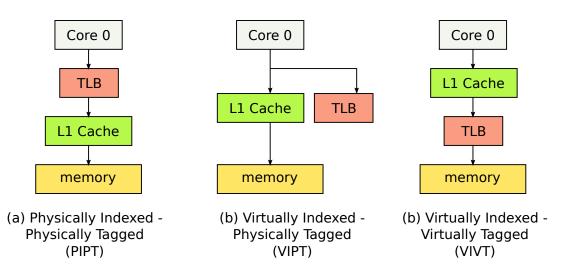

Huge pages [5, 8] increase the TLB reach by mapping very large regions with a single entry. However, huge pages need to be size-aligned in both virtual and physical address spaces, i.e., a 2 MB mapping may exist only if there is a free 2 MB-aligned page in the virtual address space that can be mapped by a free 2 MB-aligned page in the physical address space.